Western Digital Announces Plans for Its Own RISC-V Processor

RISC-V hasn’t been a huge topic for us at ExtremeTech, but the fully open-source CPU instruction set architecture (ISA) has been building momentum in the industry over the past few years as more companies have signed on to build RISC V-compatible processors. While it’s not the first open-source ISA, RISC-V is designed to be used in a wider range of devices than some of the previous work in this space. Now, Western Digital has announced that it intends to build its own RISC-V processor, in what could be a major breakthrough moment for the ISA as a whole.

RISC-V has been under development for years and is intended to be a practical ISA for CPU development rather than strictly an academic exercise.

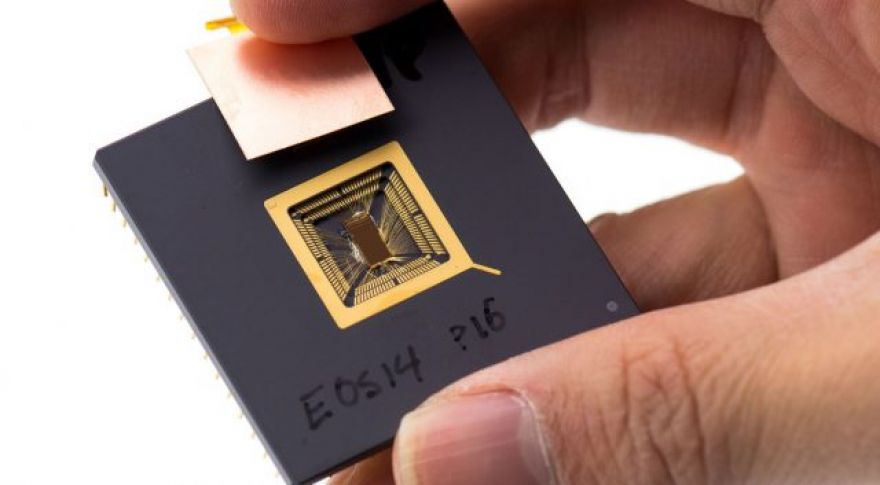

SweRV Core. Image credit: .

“As Big Data and Fast Data continues to proliferate, purpose-built technologies are essential for unlocking the true value of data across today’s wide-ranging data-centric applications,” Western Digital CTO Martin Fink in a statement. In a separate PR in late November, WD outlined some of its thinking. The company contends the era of Big Data and massive data processing workloads is less amenable to the use of general-purpose architectures to improve compute performance than it once was. Western Digital believes this one-size-fits-all approach to processing is less compatible with the demands of the modern era than what are sometimes called “domain specific architectures.”

RISC-V is Western Digital’s way of looking for a performance advantage with a CPU architecture it can customize to its own needs rather than attempting to fit into a general-purpose CPU. Of course, the kind of processing we’re referring to is fairly low level — the SweRV core is expected to be deployed in SSD and flash controllers, not a traditional CPU socket. This new CPU core is a 32-bit in-order design, with a 2-way superscalar architecture and a nine-stage pipeline. Clocks are expected to be up to 1.8GHz built on a 28nm process node.

Now Read: , , and